System design is where product requirements become architectural decisions. It defines how functions are partitioned, how power is managed, how latency is optimized, and how silicon integrates with software, firmware, and packaging. Decisions made at this level shape not only the chip but the platform, use case, and lifecycle.

As products become more complex and application-specific, whether in automotive, AI, or edge computing, the impact of system-level thinking on semiconductor design, validation, and production has become both strategic and structural.

In this edition, let us explore how system design influences semiconductor outcomes, from architecture to test coverage, power budgets to packaging formats.

How System Design Influences Silicon Architecture

System-level requirements set the foundation for what the chip must achieve and how efficiently it must operate within a broader platform.

These requirements are often defined regarding workload profiles, latency expectations, power budgets, thermal constraints, and interface compatibility. From these constraints emerge critical architectural tradeoffs that shape the fundamental structure of the silicon.

Some of the most direct influences include:

Processor Core Configuration: System-level performance targets and software threading models determine the choice of core count, type (in-order vs. out-of-order), ISA, and operating frequency.

Memory Hierarchy And Bandwidth Planning: System bandwidth demand and latency sensitivity shape Cache levels, coherence strategies, and external memory controller design.

Interconnect Fabric Selection: Whether it is AMBA AXI, a network-on-chip (NoC), or custom die-to-die interfaces for chiplet architectures, the interconnect must reflect expected communication patterns, arbitration needs, and throughput constraints.

Domain-Specific Accelerators: AI engines, image processors, cryptographic units, and video codecs are often introduced to meet real-time performance goals at constrained power envelopes. Their presence, data flow, and shared resource access are all system-driven.

Clock And Power Domain Partitioning: To meet dynamic power scaling and low-power idle targets, chips are often segmented into multiple clock and voltage islands, each aligned with functional isolation and system mode behavior.

Thus, system architects and silicon architects have to work in close alignment, from early platform modeling through RTL and floor planning.

Basic Flow To Show How System Requirements Translates Into Physical Design

Their goal is to ensure that the microarchitecture supports function and system use cases, enabling scalable performance while remaining within system-level constraints. The result is architecture that is not only functionally complete but context-aware and purpose-built.

The Role Of System Design In Packaging And Integration

Packaging today is a system-level decision too, not a back-end task. As integration density increases and power-performance targets tighten, the choice of packaging approach is directly influenced by early architectural and platform-level considerations.

Whether opting for a monolithic SoC or a chiplet-based architecture, system design determines how functions are partitioned and how dies will communicate, both logically and physically.

System Design And Packaging Impact

System-level requirements also guide decisions around 2.5D or 3D stacking, particularly in applications where memory proximity or bandwidth is critical. Die-to-die interfaces, routing density, and interconnect strategies must align with dataflow and power delivery expectations.

Even substrate design, often treated as a layout detail, becomes a strategic element, responsible for managing signal integrity, thermal paths, and mechanical reliability under real-world use conditions.

By factoring in packaging early, system design enables better thermal performance, cleaner signal paths, and improved test access, outcomes that are increasingly essential at advanced nodes and in multi-die integration.

System Co-Design And Cross-Domain Engineering

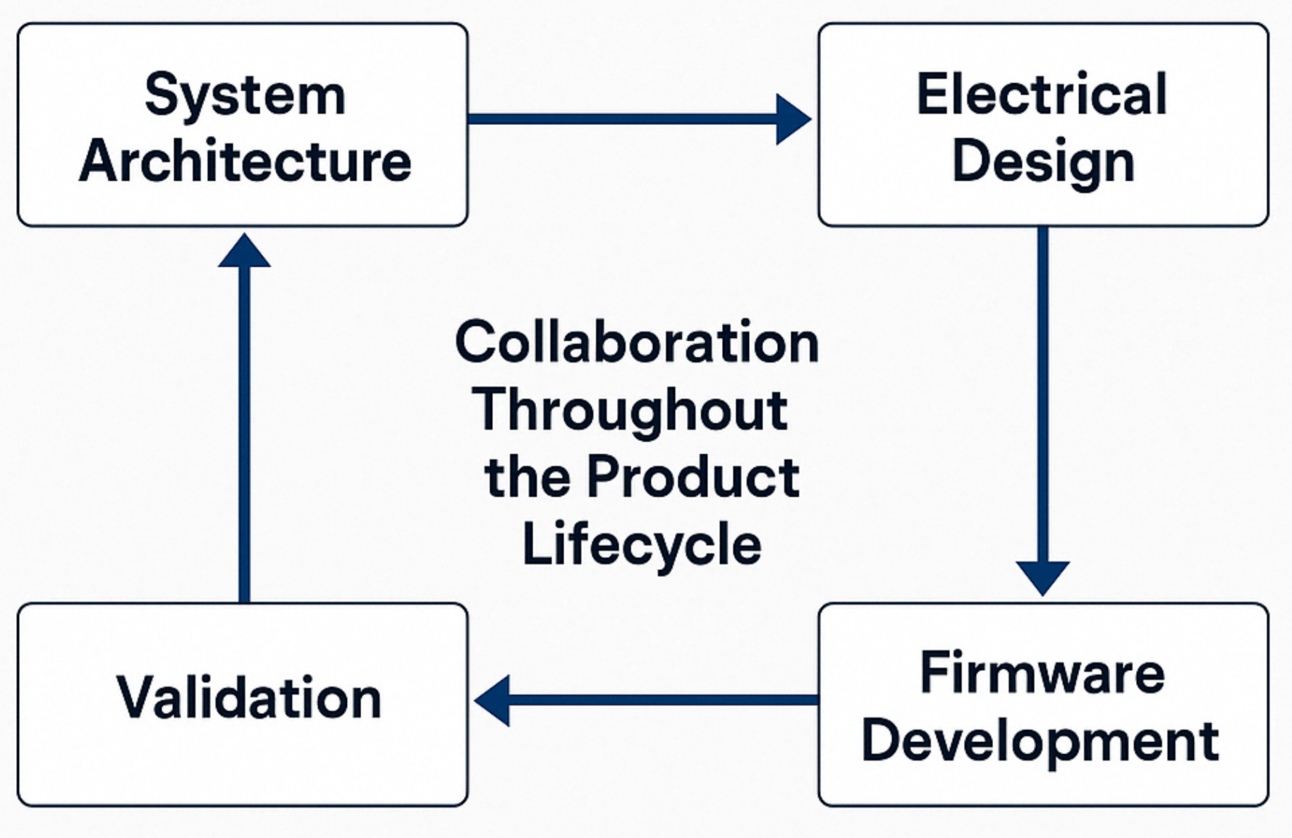

Modern system design is inherently collaborative, requiring input and alignment across electrical, mechanical, firmware, and validation domains.

This cross-disciplinary approach begins early in the product lifecycle, where system architects work alongside software and hardware teams to define not just what the product should do, but how it should behave under varying conditions, workloads, and usage environments.

Cross-Collaboration Is Key To System Design

This coordination results in tighter integration between hardware-software co-verification, firmware instrumentation for debug and performance monitoring, and design-for-test strategies that are informed by real system observability.

System-level simulations, conducted well before tape-out, help catch integration issues that would otherwise surface late in validation. Co-design minimizes rework, improves test coverage, and enables faster, more confident product delivery.

How Power And Thermal Budgets Shape System Design

System design is central in defining power and thermal budgets, often long before RTL is finalized or silicon is laid out. These constraints are not abstract, they stem directly from the product’s usage environment, form factor, and energy profile.

Whether a device is intended for a passively cooled embedded system or a high-performance mobile platform, its system-level energy target frames every downstream design decision.

Example Flow Of System Design From Power, Thermal And Architecture Requirements

Power architecture begins with defining dynamic power domains, voltage islands, and the logic required to support power gating, retention, and sleep modes. Thermal considerations like interface materials, heat spreader design, and airflow strategy are defined alongside electrical planning to ensure the final implementation meets performance and reliability expectations.

These upstream decisions directly impact silicon-level implementation, from floor planning and standard cell selection to clock tree synthesis and how test modes are aligned with power rails. By defining power behavior at the system level, teams ensure the silicon is not only functional but deployable within its intended environment.

System Validation Drives Test Strategy

System validation is no longer a post-silicon activity, it now shapes test strategy from the earliest stages of design. As chips become tightly integrated into complex systems, test planning must reflect how these devices behave in real-world conditions, not just in isolation.

System use cases, boot sequences, and dynamic interactions all influence what needs to be observable, controllable, and verifiable during test.

System Validation Integrates Deeply Into Test Strategy

This shift drives changes in how built-in self-test (BIST) logic is structured, how DFT is inserted, and how functional test content is developed. Tests are increasingly aligned with firmware access patterns, interface protocols, and operational modes defined at the system level.

As a result, the boundaries between validation and production test are narrowing, and successful silicon now depends on how well the test strategy captures the nuances of system behavior.

How System Design Shapes Lifecycle Planning

System design is not just about performance and integration, it fundamentally shapes how a semiconductor device will behave, adapt, and remain viable across its entire operational lifetime. As systems are increasingly deployed in long-use, safety-critical, and field-upgradable environments, lifecycle planning must be embedded from the start of architectural definition, not treated as a post-deployment concern.

System Design Drives Lifecycle Planning And Strategies

Moreover, system design determines how lifecycle policies are enforced across devices in the field, what gets logged, what can be updated remotely, how devices are authenticated over time, and how failures are detected before they affect operation.

This influences architectural choices such as:

Inclusion of secure elements or root-of-trust blocks

Partitioning of logic into safety and non-safety domains

Isolation strategies for fault containment and domain recovery

Hardware-enforced limits on power, thermal, and timing excursions

In modern semiconductor development, the product is not defined only by what it does at launch; it is increasingly defined by how reliably it performs years later in diverse, changing, and often unpredictable environments. System design shapes that reality from day one.

Takeaway

Ultimately, system design decisions echo through every stage of semiconductor development. From architectural block definition to packaging, power planning to validation coverage, system-level thinking shapes what the silicon must support and how reliably it must operate.

By engaging early with system architects, semiconductor engineers can build more resilient, scalable, and application-aware products.

CONNECT

Whether you are a student with the goal to enter semiconductor industry (or even academia) or a semiconductor professional or someone looking to learn more about the ins and outs of the semiconductor industry, please do reach out to me.

Let us together explore the world of semiconductor and the endless opportunities:

And, do explore the 300+ semiconductor-focused blogs on my website.