Semiconductor validation is an essential step in the product development lifecycle. It ensures that chips meet functional, electrical, and reliability requirements before mass production.

With increasing chip complexity, driven by AI accelerators, automotive ICs, and 3D-stacked designs, validation is more crucial than ever. The process involves extensive testing under different conditions to verify design accuracy, detect potential defects, and ensure compliance with JEDEC, AEC-Q100, and other industry standards.

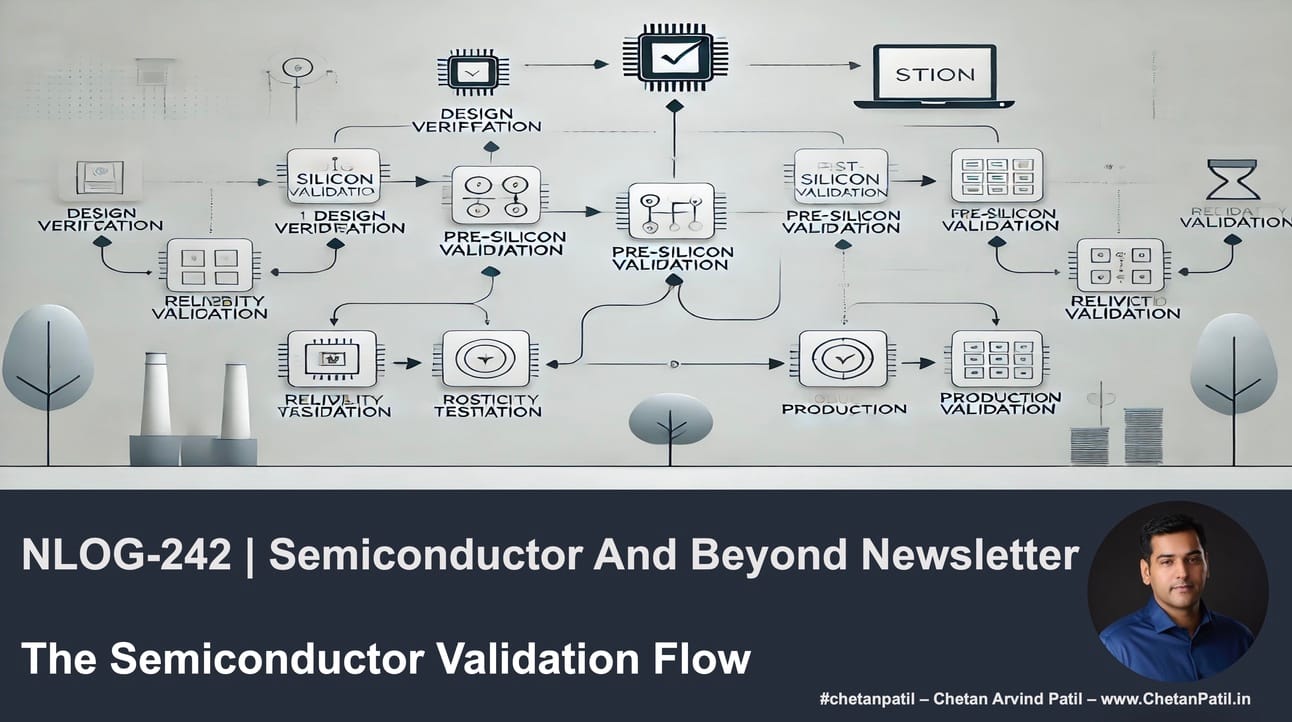

This edition explores the semiconductor validation flow, covering key phases, methodologies, and industry best practices.

What Is Semiconductor Validation?

Semiconductor validation is a systematic process of verifying and qualifying a chip’s design, performance, and reliability. The goal is to detect functional issues, electrical failures, and performance inconsistencies before mass production.

Validation is not the same as verification, while verification ensures that the design meets specifications before fabrication, validation confirms that the physical silicon meets real-world performance expectations.

The validation flow typically includes functional validation, electrical characterization, reliability testing, and compliance checks, ensuring the chip meets customer and industry requirements.

The Semiconductor Validation Flow: Key Stages

The semiconductor validation process is divided into pre-silicon and post-silicon validation, ensuring that chips meet design specifications before and after fabrication.

Pre-silicon validation occurs before the chip is manufactured, using Electronic Design Automation (EDA) tools to simulate design behavior, logic correctness, and power performance. This stage involves RTL simulation, formal verification, static timing analysis, and power estimation. By identifying functional errors and timing violations early, pre-silicon validation helps reduce the likelihood of costly silicon re-spins, ensuring a more robust design before fabrication begins.

Once the chip is fabricated, post-silicon validation is conducted on the first silicon (engineering samples) to verify that the hardware matches the intended design and functions correctly under real-world conditions. This phase focuses on ensuring performance, power efficiency, and reliability compliance, addressing potential variations introduced during manufacturing. By rigorously testing the physical chip, post-silicon validation helps detect unexpected defects, performance inconsistencies, and system-level integration issues, ensuring that the semiconductor product is ready for mass production.

Pre-Silicon Validation Phases:

Pre-silicon validation ensures that a chip's design is functionally correct, meets performance targets, and is optimized for power efficiency before fabrication. This phase relies on simulation, formal verification, and static analysis to detect design flaws early, reducing the likelihood of silicon re-spins.

Validation Stage | Purpose | Common Methods & Tools |

|---|---|---|

RTL Simulation And Functional Verification | Ensures the design logic behaves as expected before synthesis. | SystemVerilog/UVM, testbenches, constrained-random testing, assertion-based verification. |

Formal Verification | Mathematically proves design correctness without requiring test vectors. | Model checking, equivalence checking, theorem proving. |

Static Timing Analysis (STA) | Ensures the design meets timing constraints under different process, voltage, and temperature (PVT) conditions. | PrimeTime, Tempus, clock tree analysis, setup/hold timing checks. |

Power And Performance Estimation | Analyzes power consumption and evaluates architecture performance. | Power simulation tools (e.g., PowerArtist, Joules), cycle-accurate performance modeling. |

Design-For-Testability (DFT) Analysis | Embeds test structures to improve fault coverage in post-silicon testing. | Scan chain insertion, ATPG pattern generation, JTAG/BIST integration. |

Post-Silicon Validation Phases:

Post-silicon validation ensures that a fabricated chip functions as intended, meet electrical and performance specifications, and operates reliably under real-world conditions. This phase involves bring-up, functional testing, electrical characterization, system-level validation, and reliability assessments to detect deviations from the expected design. By thoroughly evaluating the silicon across different operating conditions, post-silicon validation helps identify manufacturing variations, latent defects, and integration issues, reducing the risk of failures in high-volume production.

Validation Stage | Purpose | Common Tests |

|---|---|---|

Bring-Up And Functional Validation | Ensures the chip powers up and operates as expected. | Initial power-on tests, functional boot checks, basic I/O testing. |

Electrical And Parametric Validation | Evaluates voltage, current, signal integrity, and performance under different conditions. | Voltage margining, clock jitter, thermal performance, dynamic voltage scaling. |

System-Level Validation | Verifies chip operation in an actual system with firmware and software. | System boot, peripheral integration, firmware stress tests, high-speed communication validation. |

Reliability Testing | Ensures long-term durability under environmental stress. | Burn-in tests, high-temperature operating life (HTOL), temperature cycling. |

Compliance And Certification | Confirms adherence to industry standards. | AEC-Q100 (automotive), JEDEC JESD47 (reliability), ISO 26262 (safety). |

Challenges In Semiconductor Validation

As semiconductor technology advances, validation complexity escalates, driven by shrinking process nodes, higher transistor densities, and heterogeneous architectures, the shift toward chiplet-based designs, high-speed interconnects, and AI-driven computing introduces new challenges beyond traditional methodologies. Achieving first-pass silicon success requires addressing functional correctness, electrical integrity, thermal behavior, and system-level interactions.

The following are key challenges in semiconductor validation and strategies to address them.

Increasing Chip Complexity: The transition to heterogeneous integration, chiplets, and AI processors has significantly increased validation demands. Multi-domain architectures combining analog, digital, RF, and high-speed interfaces require advanced methodologies to manage signal integrity, power interactions, and cross-chip latency. High-speed interconnects like PCIe, SerDes, DDR, and RF circuits further complicate timing and jitter analysis, making validation more challenging.

Time-To-Market Pressure: Validation must be fast and efficient with compressed product cycles to avoid delays that impact competitiveness. Design iterations, first silicon validation, and qualification must be accelerated using automated frameworks, machine learning-assisted debugging, and parallel test methodologies to reduce debugging time and ensure faster production readiness.

Cost of Validation: Post-silicon validation relies on expensive test setups, including ATE, high-speed oscilloscopes, logic analyzers, and thermal chambers. As process nodes shrink and packaging complexity increases (e.g., 2.5D, 3D stacking), test infrastructure costs rise. Engineers mitigate costs using statistical sampling, dynamic test pattern generation, and AI-driven anomaly detection to optimize validation coverage without excessive resource usage.

Power And Performance Optimization: Meeting power efficiency targets while ensuring performance scalability requires extensive testing across voltage, temperature, and frequency variations. Dynamic voltage scaling (DVS), adaptive clocking, and power gating add further complexity, requiring corner-case validation, hardware-in-the-loop (HIL) simulations, and real-time power monitoring to ensure stable operation under real-world conditions.

To overcome these challenges, semiconductor companies integrate AI-driven test automation, digital twin simulations, and real-time analytics into their validation strategies. AI-assisted data analysis helps detect failure patterns faster, while digital twin models enable pre-silicon validation to match post-silicon results closely. These innovations are helping reduce validation cycles, improve first-pass silicon success rates, and ensure robust semiconductor performance in production.

The semiconductor industry can mitigate these challenges by adopting a more automated, predictive, and data-driven approach. This approach would improve validation efficiency and accelerate the time to market for next-generation chips.

Takeaway

Semiconductor validation ensures that a chip meets functional, electrical, and reliability requirements before mass production.

Pre-silicon validation prevents significant design errors before fabrication, reducing the risk of costly revisions. Post-silicon validation verifies real-world chip performance across various conditions to ensure compliance with industry standards.

Key validation phases include functional, electrical, system, and reliability testing, each crucial in identifying defects and optimizing performance. Emerging trends such as AI-driven validation and digital twin simulations are transforming the way semiconductor testing is conducted, improving efficiency and accuracy.

Without a robust validation strategy, semiconductor companies face silicon re-spins, increased costs, and market delays. Optimizing validation methodologies is essential for achieving first-pass silicon success and ensuring competitive product development.

CONNECT

Whether you are a student with the goal to enter semiconductor industry (or even academia) or a semiconductor professional or someone looking to learn more about the ins and outs of the semiconductor industry, please do reach out to me.

Let us together explore the world of semiconductor and the endless opportunities:

And, do explore the 300+ semiconductor-focused blogs on my website.